- 您现在的位置:买卖IC网 > Sheet目录1991 > CS5368-DQZ (Cirrus Logic Inc)IC ADC 8CH 114DB 216KHZ 48-LQFP

16

DS624F4

CS5368

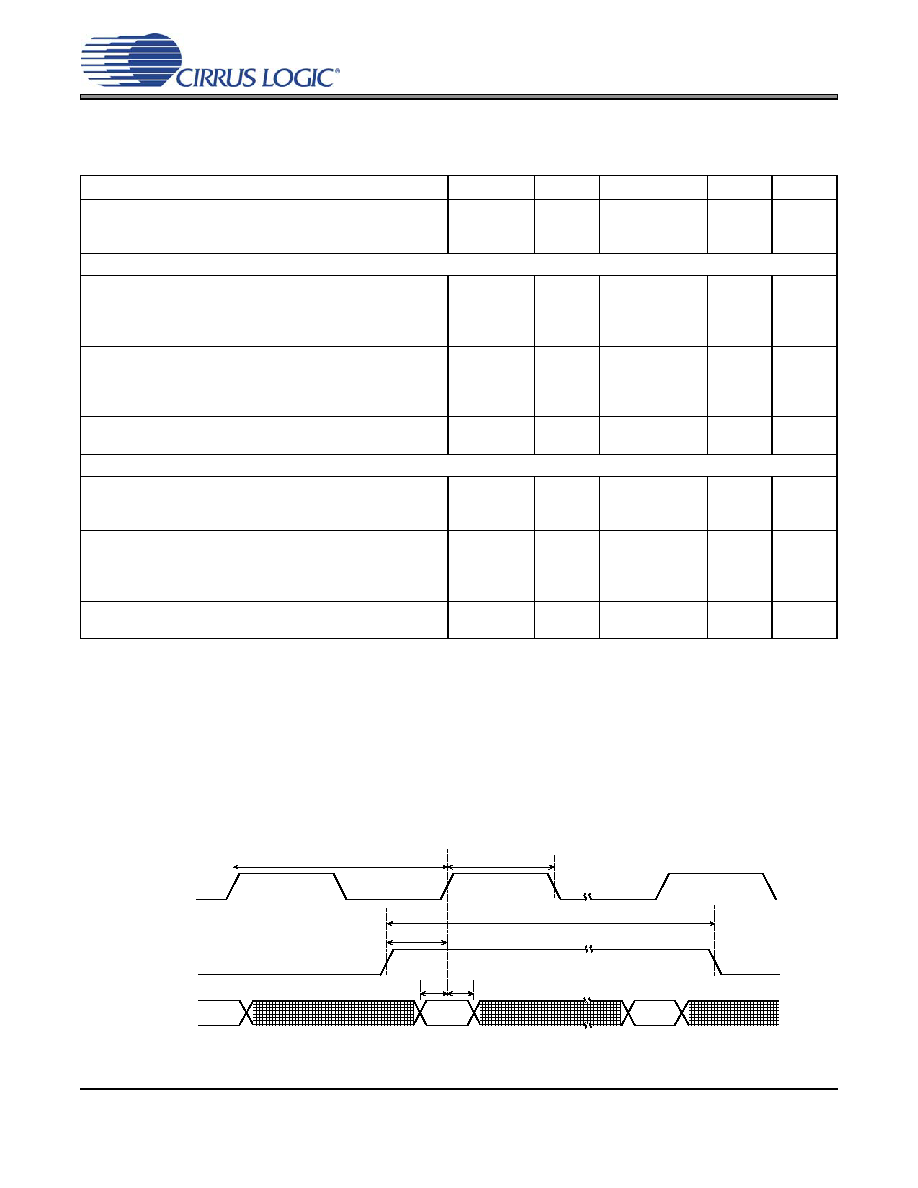

SERIAL AUDIO INTERFACE - TDM TIMING

The serial audio port is a three-pin interface consisting of SCLK, LRCK and SDOUT.

Logic "0" = GND = 0 V; Logic "1" = VLS; CL = 20 pF, timing threshold is 50% of VLS.

Notes:

1.

TDM Quad-Speed Mode only specified to operate correctly at VLS

≥ 3.14 V.

2.

Duty cycle of generated SCLK depends on duty cycle of received MCLK as specified under “System

3.

CLKMODE functionality described in Section 4.6.3

4.

In Slave Mode, the SCLK/LRCK ratio can be set according to preference; chip performance is guaran-

teed only when using the ratios in Section 4.7 Master and Slave Clock Frequencies on page 25.

Figure 4. TDM Timing

Parameter

Symbol

Min

Typ

Max

Unit

Sample Rates

Single-Speed Mode

Double-Speed Mode

Quad-Speed Mode1

-

2

54

108

-

54

108

216

kHz

Master Mode

SCLK Frequency

SCLK Period

1/(256*216 kHz)

SCLK Duty Cycle (Note 2)

(CLKMODE = 0)(Note 3)

(CLKMODE = 1)(Note 3)

tPERIOD

tHIGH1

256*Fs

18

40

28

-

50

33

256*Fs

-

60

38

Hz

ns

%

FS setup

before SCLK rising (Single-Speed Mode)

FS setup

before SCLK rising (Double-Speed Mode)

FS setup

before SCLK rising (Quad-Speed Mode)

FS width

in SCLK cycles

tSETUP1

tHIGH2

20

18

5

128

-

128

ns

-

SDOUT setup

before SCLK rising

SDOUT hold

after SCLK rising

tSETUP2

tHOLD2

5

-

ns

Slave Mode

SCLK Frequency (Note 4)

SCLK Period

1/(256*216 kHz)

SCLK Duty Cycle

tPERIOD

tHIGH1

-

18

28

256*Fs

-

65

Hz

ns

%

FS setup

before SCLK rising (Single-Speed Mode)

FS setup

before SCLK rising (Double-Speed Mode)

FS setup

before SCLK rising (Quad-Speed Mode)

FS width

in SCLK cycles

tSETUP1

tHIGH2

20

10

1

-

244

ns

-

SDOUT setup

before SCLK rising

SDOUT hold

after SCLK rising

tSETUP2

tHOLD2

5

-

ns

FS

SDOUT

SCLK

data

t

HOLD2

t

SETUP2

t

SETUP1

new frame

data

t

PERIOD

t

HIGH1

t

HIGH2

发布紧急采购,3分钟左右您将得到回复。

相关PDF资料

CS5381-KSZ

IC ADC AUD 120DB 192KHZ 24-SOIC

CS53L21-CNZR

IC ADC STEREO 24BIT 98DB 32-QFN

CS5509-ASZR

IC ADC 16BIT SGL SUPP 16-SOIC

CS5512-BSZ

IC ADC 20BIT EXTERNAL OSC 8-SOIC

CS5526-BSZR

IC ADC 20BIT W/4BIT LATCH 20SSOP

CS5528-ASZR

IC ADC 24BIT 8CH 24-SSOP

CS5529-ASZR

IC ADC 16BIT W/6BIT LATCH 20SSOP

CS5530-ISZR

IC ADC 24BIT 1CH W/LNA 20-SSOP

相关代理商/技术参数

CS5368-DQZR

功能描述:音频模/数转换器 IC IC 114dB 192kHz 8ch ADC w/TDM Intrfc RoHS:否 制造商:Wolfson Microelectronics 转换速率: 分辨率: ADC 输入端数量: 工作电源电压: 最大工作温度: 最小工作温度: 安装风格: 封装 / 箱体: 封装:

CS5371

制造商:CIRRUS 制造商全称:Cirrus Logic 功能描述:Low-power, High-performance ΔΣ Modulators

CS5371_05

制造商:CIRRUS 制造商全称:Cirrus Logic 功能描述:Low-power, High-performance ΔΣ Modulators

CS5371A

制造商:CIRRUS 制造商全称:Cirrus Logic 功能描述:Low-power, High-performance Modulators

CS5371A_09

制造商:CIRRUS 制造商全称:Cirrus Logic 功能描述:Low-power, High-performance ΔΣ Modulators

CS5371A-IS

功能描述:接口 - 专用 LP High Performance Delta Sigma Mod. RoHS:否 制造商:Texas Instruments 产品类型:1080p60 Image Sensor Receiver 工作电源电压:1.8 V 电源电流:89 mA 最大功率耗散: 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:BGA-59

CS5371A-ISR

功能描述:模数转换器 - ADC LP High Performance Delta Sigma Mod. RoHS:否 制造商:Texas Instruments 通道数量:2 结构:Sigma-Delta 转换速率:125 SPs to 8 KSPs 分辨率:24 bit 输入类型:Differential 信噪比:107 dB 接口类型:SPI 工作电源电压:1.7 V to 3.6 V, 2.7 V to 5.25 V 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:VQFN-32

CS5371A-ISZ

功能描述:接口 - 专用 IC LP Hgh Prfrmnc Delta Sigma Modultr RoHS:否 制造商:Texas Instruments 产品类型:1080p60 Image Sensor Receiver 工作电源电压:1.8 V 电源电流:89 mA 最大功率耗散: 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:BGA-59